ケイデンスがチップレット開発を加速するパートナーエコシステムを発表

半導体設計の分野で世界をリードするケイデンスは、2026年1月6日(米国時間)に、AI(人工知能)、データセンター、HPC(高性能コンピューティング)向けのチップレット開発を加速するための「Chiplet Spec-to-Packaged Partsエコシステム」を発表しました。このエコシステムは、チップレット設計における複雑さを軽減し、製品が市場に投入されるまでの期間を大幅に短縮することを目的としています。

チップレットとは?なぜ今、注目されているのか?

チップレットとは、複数の小さな半導体チップ(ダイ)を組み合わせて一つの大きな高性能な半導体パッケージとして機能させる技術のことです。従来の半導体製造では、一つの大きなチップ(SoC:System on a Chip)として設計・製造するのが一般的でした。しかし、高性能化が進むにつれて、大きなチップを製造する際のコストや歩留まり(不良品の少なさ)の問題が顕著になってきました。

チップレット技術は、この課題を解決する鍵として注目されています。小さなチップをそれぞれ最適なプロセスで製造し、それらを組み合わせることで、以下のようなメリットが期待できます。

-

コスト削減: 大規模なチップを一度に製造するよりも、小さなチップを複数製造する方が製造コストを抑えられる可能性があります。

-

柔軟性の向上: 必要な機能に応じてチップレットを組み合わせることで、特定の用途に特化した半導体を効率的に開発できます。

-

性能向上: 最新の技術で製造された高性能なチップレットを組み合わせることで、より高い処理能力を持つ半導体を構築できます。

-

市場投入期間の短縮: 既存のチップレットを再利用することで、ゼロから設計するよりも開発期間を短縮できます。

AIの進化やデータセンターの需要増加に伴い、半導体にはさらなる高性能化と効率化が求められています。チップレットは、これらの要求に応えるための重要な技術として、今後ますますその存在感を増していくでしょう。

ケイデンスの「Chiplet Spec-to-Packaged Partsエコシステム」の概要

ケイデンスが発表したこのエコシステムは、チップレットの設計からパッケージングまでを一貫してサポートし、さまざまな企業が協力し合うことで、チップレットの導入をよりスムーズに、そして迅速に進めることを目指しています。

このエコシステムには、初期のIP(知的財産)提供パートナーとして、Arm社、Arteris社、eMemory社、M31 Technology社、Silicon Creations社、Trilinear Technologies社が参加しています。また、半導体解析技術のパートナーとしてはproteanTecs社が名を連ねています。

リスクを低減し、チップレットの採用を円滑にするため、ケイデンスはSamsung Foundryと協力し、Samsung FoundryのSF5Aプロセスを活用して、パートナー各社から提供されたIPを事前統合した「Cadence® Physical AIチップレットプラットフォーム」を基盤とした半導体試作品のデモを構築する予定です。これにより、実際の製品開発における検証の負担を軽減し、開発期間の短縮に貢献します。

Arm社との戦略的協業でAI分野のイノベーションを加速

ケイデンスとArm社は、長年にわたる密接な協力関係をさらに強化し、フィジカルAI(物理世界とAIの融合)およびインフラAI(AIを活用したインフラ管理など)の分野におけるイノベーション加速に取り組んでいます。

ケイデンスは今後、Arm® Zena™ Compute Subsystem(CSS)やその他の主要なIPを活用して、Physical AIチップレットプラットフォームおよびChiplet Frameworkを強化します。これにより、自動車、ロボティクス、ドローンといった次世代のエッジAI(デバイス側でAI処理を行う技術)に必要な処理能力だけでなく、データセンター、クラウド、HPCで求められる標準I/Oやメモリチップレットのニーズにも対応できるようになります。

この協業は、設計の複雑さを軽減し、低リスクで先進的なチップレットの導入を可能にすることで、よりスマートで安全、かつ効率的なシステムの実現を後押しすると考えられます。

ケイデンスのチップレットフレームワークアーキテクチャ

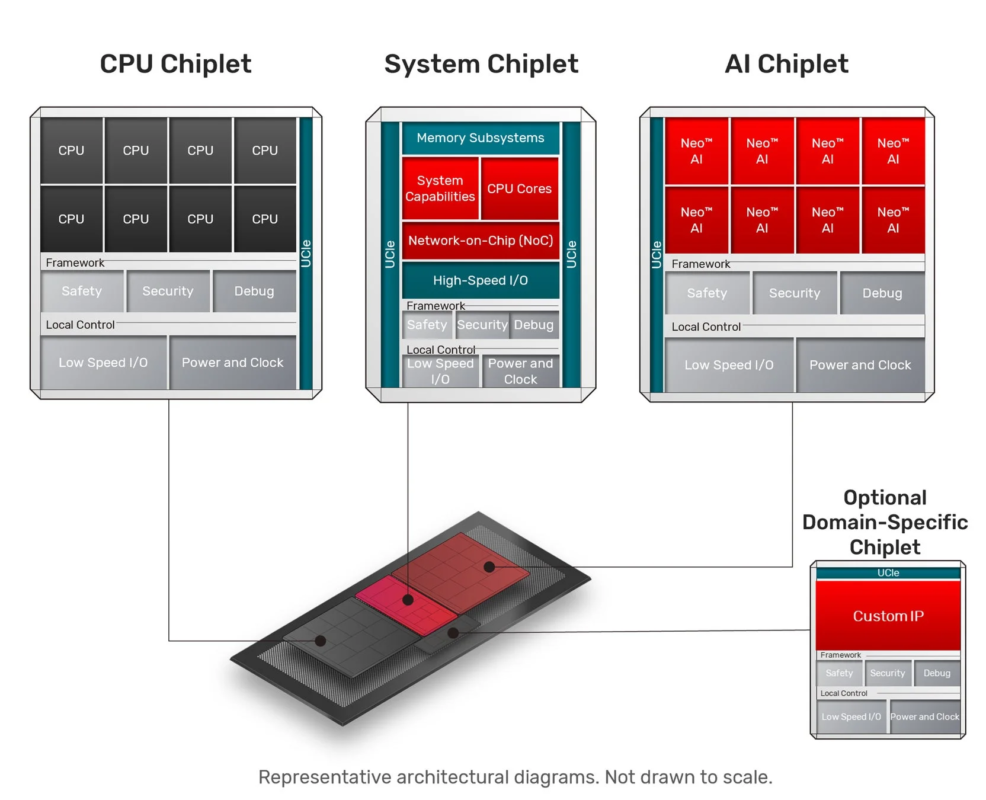

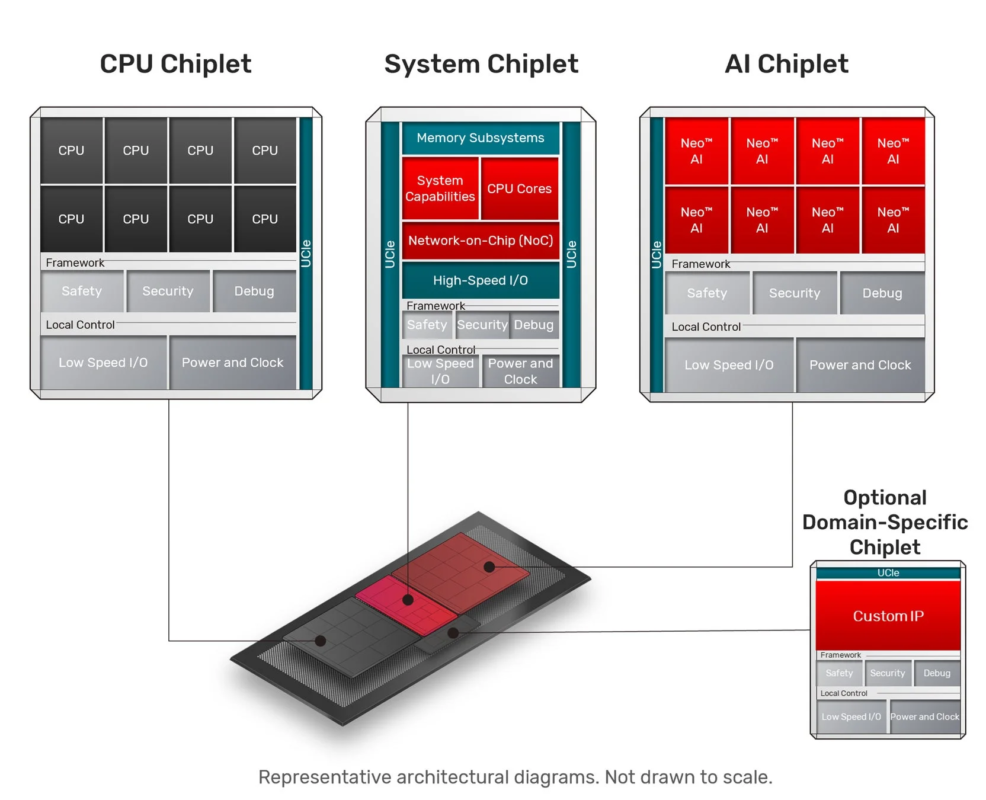

ケイデンスは、仕様に基づく自動化技術を用いて、自社およびサードパーティパートナーのIPに、チップレット管理、セキュリティ、安全機能を組み合わせたチップレットフレームワークアーキテクチャを構築しています。

このフレームワークによって生成されるEDA(Electronic Design Automation:半導体設計自動化)フローは、Cadence Xcelium™ Logic Simulatorによるシミュレーションや、Cadence Palladium® Z3 Enterprise Emulation Platformによるエミュレーションをシームレスに実現します。また、物理設計フローにおいては、リアルタイムフィードバックを通じて効率的な配置配線プロセスを可能にします。

生成されるチップレットアーキテクチャは、Arm Chiplet System Architectureや今後策定されるOCP Foundational Chiplet System Architectureなどの業界標準に準拠しており、エコシステム全体での広範な相互運用性を確保します。さらに、ケイデンスのUniversal Chiplet Interconnect Express™(UCIe™)IPは業界標準のダイ間接続を実現し、LPDDR6/5X、DDR5-MRDIMM、PCI Express®(PCIe®)7.0、HBM4といった最先端インターフェースの迅速な統合を可能にする包括的なプロトコルIPポートフォリオを提供します。

Cadence Physical AIチップレットプラットフォームの一部であるベースシステムチップレットの初期プロトタイプは、ケイデンスのチップレットフレームワーク、UCIe 32G、LPDDR5X IPを組み込み、すでにシリコンでの完全な検証が完了しています。これにより、技術の実現性と信頼性が実証されています。

パートナー各社からのコメント

本エコシステムに参加する各社の代表者からは、期待と協力への意欲を示すコメントが寄せられています。

Arm社 Suraj Gajendra氏

「自動車やロボティクスといった新興分野で計算処理の需要が急増する中、業界は高性能・高効率・機能安全を設計段階から実現できる拡張性の高いソリューションを求めています。Arm Zena CSSの活用により、ケイデンスのチップレットプラットフォームは次世代インテリジェントシステムの要件を満たし、フィジカルAI分野の進化とチップレット導入の加速、そして設計の複雑さの軽減に貢献します。」

Arteris社 Guillaume Boillet氏

「イノベーションを牽引する当社のネットワークオンチップIP製品(Ncore、FlexNoC)が、ケイデンスのPhysical AI Chiplet PlatformとChiplet Frameworkをサポートできることを大変嬉しく思います。ケイデンスと共に、高帯域幅でスケーラブル、量産実績のあるインターコネクト技術を活用し、次世代マルチダイシステムにおけるチップレットアーキテクチャの採用を促進します。」

eMemory社 Charles Hsu氏

「当社の高機能OTP製品は、ケイデンスのSecuryzr™ Root of Trustと組み合わせることで、Cadence Chiplet Frameworkにおけるセキュリティを強化します。また、不揮発性メモリ技術のリーディングプロバイダーである当社の技術とケイデンスのセキュリティサブシステムを統合することで、安全なストレージと長期ライフサイクルの鍵管理を実現し、先進的なチップレット設計におけるダイ間のセキュリティと安全性を確保する強固なハードウェア基盤を提供できます。」

M31 Technology社 Scott Chang氏

「ケイデンスが拡大するチップレット・エコシステムに貢献できることを誇りに思います。本エコシステムは、最先端プロセス技術におけるインターフェースIPを継続的に進化させ、最新のMIPI規格に対応し続けています。当社は、車載グレードIPの実績と、大量生産されるコンシューマ製品を10年以上支えてきた経験を活かし、業界最高水準のMIPI PHYインターフェースIPを提供します。これにより、MIPI CSIとDSIを柔軟に統合し、先進的なチップレットソリューションを迅速に実現できます。」

proteanTecs社 Ziv Paz氏

「ケイデンスのチップレットプラットフォームと提携し、あらゆるチップレットに当社のテレメトリを組み込めることを大変嬉しく思います。ケイデンスと共に、次世代コンピューティングの需要に応える、安全性・信頼性・電力効率に優れたフィジカルAIを実現します。この協業により、車載や自動運転向けの先進的なSoCやシステムを開発するお客様に、確かな価値をお届けします。」

Samsung Electronics社 Taejoong Song氏

「ケイデンスとの協業により、当社のSF5A技術が持つ優位性を実証できることを嬉しく思います。この強固なパートナーシップを通じて、Chiplet Spec-to-Packaged Partsエコシステムの拡大を目指します。さらに、フィジカルAI分野、特に次世代車載システムの設計向けに、お客様が最先端の半導体ソリューションを迅速かつ確実に実現できるよう支援します。」

Silicon Creations社 Pawel Banachowicz氏

「ケイデンスとの長年のパートナーシップを、Chiplet Spec-to-Partsエコシステムでさらに深められることを嬉しく思います。過去15年間で、当社は主要ファウンドリ向けに100以上のカスタムPLLを開発・提供してきました。これまで高性能・低ジッターPLLや専用クロックソリューションを提供してきたこの協業を、次世代チップレット設計の加速に向けてさらに拡大できることを楽しみにしています。」

Trilinear Technologies社 Carl Ruggiero氏

「この画期的な取り組みの一環として、当社の先進的なDisplayPort IPを提供できることを大変嬉しく思います。ケイデンスとの協業により、高性能なビデオ接続を実現し、柔軟で将来対応型のディスプレイソリューションをチップレット・エコシステムに提供します。」

ケイデンスのコメントと今後の展望

ケイデンスのCompute Solutions Group担当バイスプレジデントであるDavid Glasco氏は、今回の新たなチップレット・エコシステムの発表を「チップレット活用の推進における重要なマイルストーン」と述べています。マルチダイやチップレットベースのアーキテクチャは、設計の複雑化が進む中で、より高い性能とコスト効率を達成するために不可欠な技術であると強調しました。

ケイデンスのチップレットソリューションは、コスト最適化、カスタマイズ性、そして構成の自由度を実現できると説明されています。同社の幅広いIPポートフォリオとSoC設計の専門知識に、エコシステムパートナー企業の事前統合・事前検証済みIPを組み合わせることで、チップレットベースのソリューション開発を加速し、顧客がチップレットを活用した設計目標をスムーズかつ確信を持って達成できるよう支援するとのことです。

このエコシステムは、AI半導体をはじめとする次世代の高性能半導体開発において、業界全体の協力体制を強化し、技術革新をさらに加速させる重要な役割を果たすでしょう。チップレット技術が普及することで、より多様で高性能なデバイスが、より早く市場に登場することが期待されます。

関連リソース

本プレスリリースに関する詳細情報や関連技術については、以下のリソースをご参照ください。

-

ブログ「From Spec to Silicon: Successful Physical AI System Chiplet Bring-Up」

-

ウェビナー「Chiplets Solutions: Helping You Realize Your Chiplet Ambitions」

-

ブログ「Cadence Transforms Chiplet Technology with First Arm-Based System Chiplet」

ケイデンスに関する詳細情報は、公式ウェブサイトをご確認ください。