AI時代の基盤を築く半導体技術の羅針盤

現代社会において、AI(人工知能)の進化は目覚ましく、その発展を支える中核技術が半導体です。特に、特定の用途に特化して高い性能と効率を実現する「ドメイン特化型半導体」、そして「ASIC(Application Specific Integrated Circuit)」や「SoC(System on Chip)」、さらにはAIの推論処理に特化した「AI・ML推論チップ」への注目が高まっています。

一般社団法人 次世代社会システム研究開発機構(INGS)は、これらの次世代半導体技術の動向を包括的に分析した『ドメイン特化型半導体/ASIC/SoC(System on Chip)/AI・ML推論チップ白書2026年版』を2026年1月30日に発刊しました。本白書は、AI時代の半導体エコシステムがどのように変革していくのかを詳細に解明し、2030年までの技術ロードマップと投資判断に不可欠な情報を提供します。

白書が示すAI半導体市場の驚異的な成長

本白書は、次世代半導体技術の中核となるASIC・SoCとAI/ML推論システム、そしてその他のドメイン特化型半導体に関する包括的な産業、技術、市場分析レポートです。2026年から2030年にかけての技術トレンド、市場規模、産業構造、主要プレイヤーの戦略が詳細に解説されています。

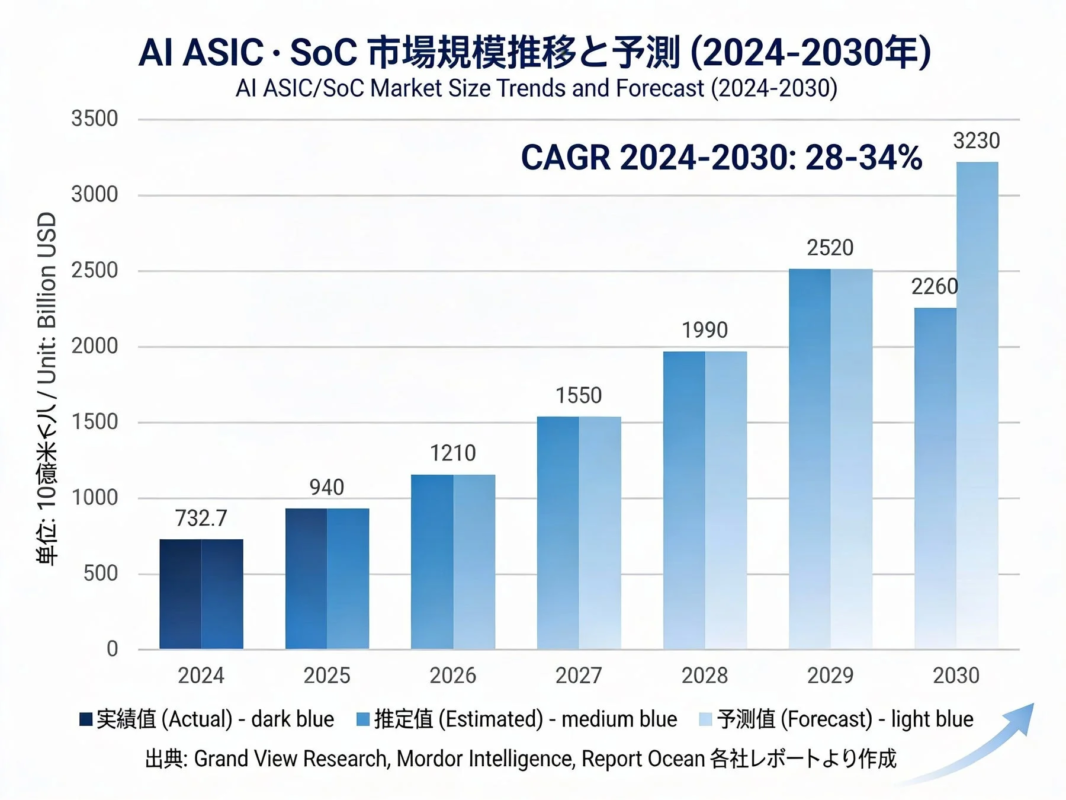

特に注目すべきは、市場規模の予測です。2024年の732.7億ドルから、2030年には2,260億ドルから最大3,230億ドルへと大きく拡大すると見込まれており、年平均成長率(CAGR)は28%から34%という高成長が予測されています。このデータは、AI関連半導体市場が今後数年間で急速に拡大することを示唆しており、関連産業にとって大きなビジネスチャンスが到来していることを物語っています。

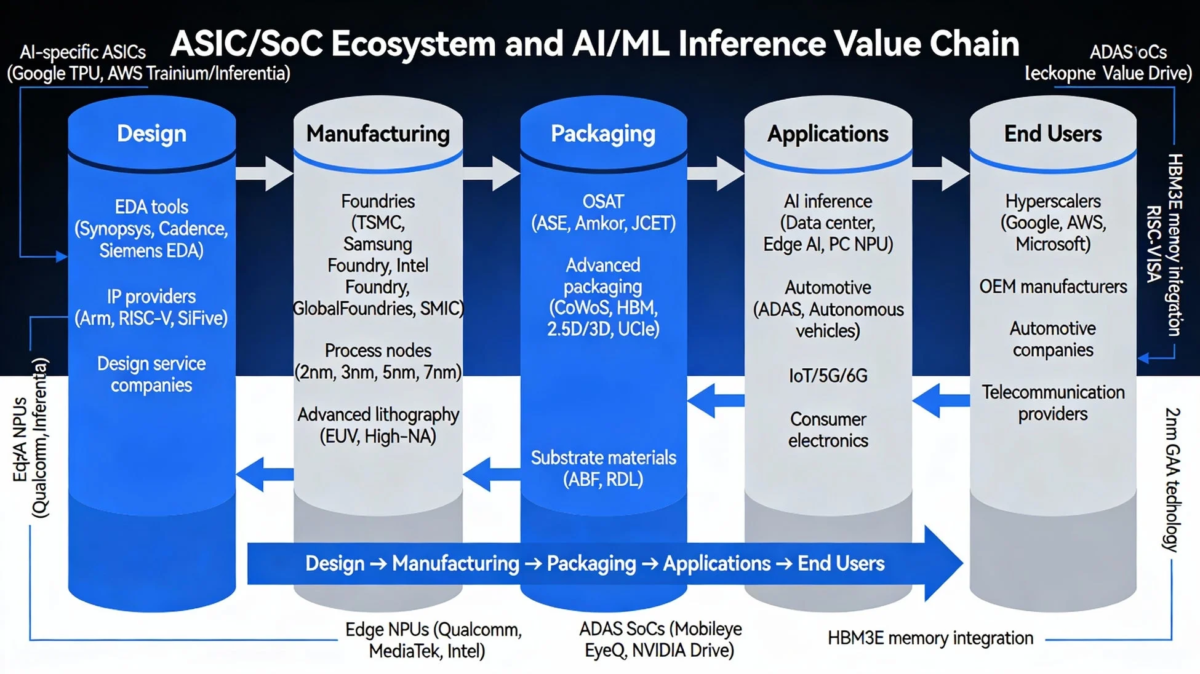

ASICとGPUの競争、Rapidusのような先端ファウンドリ(半導体受託製造企業)の戦略、HBMメモリ(広帯域幅メモリ)の需要急増、2nm/GAA技術(次世代トランジスタ構造)への移行、そしてEDA(電子設計自動化)ツール、IP(知的財産)、パッケージング技術の高度化など、半導体バリューチェーン全体の進化が戦略資料としてまとめられています。

最先端技術の動向と地政学的な視点

技術面では、世界をリードする半導体メーカー各社の取り組みが詳述されています。例えば、TSMCのCoWoS 2.5D/3Dパッケージング技術(複数のチップを効率的に統合する技術)、Samsung Foundryの3nm GAA(次世代トランジスタ構造)、Intel Foundry Servicesといった先端製造技術の動向。また、オープンソースの命令セットアーキテクチャであるRISC-V ISAの普及、Google TPUやAWS Trainium/InferentiaのようなAI専用ASIC(特定のAIタスクに特化した半導体)、エッジAI(デバイス上でAI処理を行う技術)向けのNPU(ニューラルプロセッシングユニット)、自動車の先進運転支援システム(ADAS)向けSoC、6G通信チップ、そしてフォトニクス統合(光技術と電子技術の融合)など、多岐にわたる最先端技術トレンドが解説されています。

さらに、本白書は地政学的な視点からも半導体産業を分析しています。米国CHIPS Act、EU Chips Act、日本のRapidus 2nm戦略、中国のSMIC/UNISOC、台湾のTSMC/MediaTek、韓国のSamsung/SK Hynixなど、各国・地域の半導体戦略を詳細に分析。サプライチェーンの再編とオープン戦略の重要性が示されており、国際情勢が半導体産業に与える影響を理解する上で貴重な情報源となります。

白書の多岐にわたる利用シーン

この白書は、半導体産業に関わる様々な部門で活用されることを想定して編纂されています。

戦略企画部門

-

中長期技術戦略策定: 2030年までのAI/半導体ロードマップを作成する際の重要な参照資料となります。

-

投資意思決定: ファウンドリ、EDA、IP、パッケージングといった分野への投資判断を行うための材料として役立ちます。

-

M&A検討: 半導体エコシステム内での買収や提携候補企業を評価する際のベンチマークとして活用できます。

製品開発部門

-

次世代SoC設計: AI専用ASIC、エッジNPU、自動車ADAS SoCなどの設計方針を決定する上で、最新の技術動向や市場ニーズを把握できます。

-

プロセス技術選択: 3nm/2nm/GAA/FinFETといった先端プロセス技術の採用判断や、最適なファウンドリの選定に貢献します。

-

パッケージング戦略: CoWoS、HBM、UCIe(チップレット間接続のオープン標準)などの先進的な実装技術を選択する際の指針となります。

事業開発・営業部門

-

顧客提案資料作成: AI/IoT/自動車/5G市場向けのソリューション提案時に、最新の市場データやトレンドを盛り込むことができます。

-

競合分析: NVIDIA、Google、AWS、Intel、Qualcommといった主要競合企業の戦略を詳細に分析し、自社の強みと弱みを明確化します。

-

新規事業探索: エッジAI、DPU(データプロセッシングユニット)、SmartNIC(スマートネットワークインターフェースカード)、フォトニクスなどの新興市場における機会を評価できます。

経営層・投資家向け報告

-

取締役会報告: 半導体市場のトレンドと自社のポジショニングを説明するための資料として活用できます。

-

IR資料作成: 投資家向けに半導体技術や市場動向を説明する際の客観的なデータを提供します。

-

産学連携検討: 大学や研究機関との共同研究テーマを選定する際の参考となります。

研究開発部門

-

技術ベンチマーク: EUV、High-NA、GAA、CFETなどの先端プロセス技術動向を把握し、自社の研究開発の方向性を定めます。

-

標準化活動: UCIe、RISC-V、CXL(コンピュートエクスプレスリンク)などのオープン規格への参画判断に役立ちます。

-

特許戦略: 主要企業の知財ポートフォリオを分析し、自社の特許戦略を立案する上で重要な情報源となります。

サプライチェーン管理

-

サプライヤー評価: ファウンドリ、OSAT(半導体後工程受託企業)、材料メーカーの能力や戦略を分析し、最適なサプライヤーを選定します。

-

リスク管理: 地政学リスク、供給制約、技術移行リスクなどを評価し、サプライチェーンの安定性を確保するための対策を検討します。

-

調達戦略: HBM、ABF基板、SiC/GaNなどの戦略材料の調達計画を策定する上で、市場の需給動向を把握できます。

2030年に向けた具体的なアクションプランとゴール

本白書では、短期(2026-2027年)、中期(2028-2029年)、長期(2030年以降)にわたる具体的なアクションプランと提言骨子が示されています。

短期施策(2026-2027年)

-

AI専用ASIC戦略の明確化: GPUへの依存を減らし、自社のワークロードに最適化されたASICの開発を検討します。また、QualcommやMediaTekに続くPC/モバイルAI市場へのエッジNPU参入を目指します。

-

先端パッケージング技術の採用: CoWoS/HBM実装を早期に導入し、AI/HPC(高性能コンピューティング)向け高性能製品での競争力を確保します。TSMCとの戦略的パートナーシップを強化し、先端ノードへの優先アクセスを目指します。

-

RISC-V ISA活用の推進: Arm代替戦略を検討し、ロイヤリティ削減とカスタマイズの自由度向上を図ります。SiFive/Andesなどとの提携により、成熟したIPを活用し開発期間を短縮します。

-

自動車ADAS SoC強化: ASIL D準拠チップの開発を通じてISO 26262(自動車機能安全規格)対応プロセスを確立し、MobileyeやNVIDIAとの競合において差別化ポイントを明確にします。

中期施策(2028-2029年)

-

2nm/GAA技術への移行準備: EDA/IP/DFT(設計検証)ツールの整備を進め、先端ノードに対応した設計環境を構築します。Rapidus戦略を評価し、日本国内の2nmファウンドリの活用可能性を検討します。

-

エッジAI市場での差別化: 低消費電力AI推論チップ(15W以下NPU/ASIC)の製品化を目指し、TinyML/SLM(Small Language Model)対応によるオンデバイスAIの本格展開を図ります。

-

UCIe/CXL等のオープン標準採用: チップレット戦略を推進し、開発コスト削減と柔軟性向上を実現します。Intel/AMD/TSMCなどとのエコシステム連携を強化します。

-

フォトニクス技術の研究開発: Co-Packaged Optics (CPO)の検討により、データセンター向け次世代インターコネクト技術を追求します。シリコンフォトニクスIPの獲得を、自社開発または戦略的M&Aを通じて目指します。

長期施策(2030年以降)

-

AI時代の半導体アーキテクチャ確立: メモリ内演算(IMC)技術やニューロモルフィックチップ(脳型チップ)の商用化により、SNN(スパイクニューラルネットワーク)アーキテクチャの実現を目指します。

-

地政学対応とサプライチェーン多様化: CHIPS Act/EU Chips Actを活用した地域分散生産体制を構築し、HBM、ABF、SiC/GaNなどの重要部材の戦略的在庫確保を進めます。

-

Beyond CMOS技術の探索: CFET/3D積層トランジスタなどの1nm世代への対応技術や、量子コンピューティング連携によるハイブリッドアーキテクチャの研究を進めます。

-

持続可能性とグリーンAI: AI推論の電力効率を10倍向上させる目標を掲げ、低消費電力設計手法を確立します。ライフサイクルアセスメント(LCA)に基づいた環境負荷低減戦略を推進します。

これらの施策を通じて、白書は以下のゴール達成を目指します。

-

戦略的意思決定の加速: 2030年までの半導体技術ロードマップを明確化し、AI時代における自社ポジショニングを再定義します。投資・M&A・提携の優先順位付けを支援します。

-

技術選択の最適化: プロセスノード選択、パッケージング技術、ISA(命令セットアーキテクチャ)選択の根拠を確立します。

-

市場機会の発見: AI ASIC、エッジNPU、ADAS SoCなどの成長市場への参入を促し、DPU、SmartNIC、フォトニクスなどの新興分野への先行投資を支援します。

-

競争優位性の構築: 主要競合の戦略を理解し、差別化ポイントの明確化と技術投資の集中を促します。

-

リスク管理の強化: 地政学リスクやサプライチェーン制約、技術移行リスクへの対応策を強化します。

-

組織能力の向上: 技術トレンドに関する組織全体のリテラシーを向上させ、データに基づく客観的な議論を促進します。

白書の詳細と購入方法

『ドメイン特化型半導体/ASIC/SoC(System on Chip)/AI・ML推論チップ白書2026年版』は、A4判1,800ページに及ぶ大ボリュームのレポートです。一般社団法人 次世代社会システム研究開発機構が監修・発行し、2026年1月30日に発刊されました。

本白書は、製本版とPDF版が提供されており、PDF版はeメールまたはダウンロードでの納品にも対応しています。

詳細情報および購入については、以下のリンクをご参照ください。

一般社団法人 次世代社会システム研究開発機構は、長年にわたり産業、先進先端技術、経済・経営、IT分野のシンクタンク活動を展開しており、その刊行物は国内外の多くの機関で高く評価されています。本白書も、半導体産業の未来を洞察するための重要な資料となるでしょう。